Application IP Subsystem

Application IP subsystems are an essential component of a System-on-Chip (SoC). They are pre-designed blocks of intellectual property that are used to implement specific functions within the SoC. Application IP subsystems can be designed to perform a wide range of functions, from audio and video processing to connectivity and security.

The purpose of an application IP subsystem is to provide a complete, pre-verified solution for a specific application or function. These subsystems are designed to be modular and can be integrated into the SoC design as needed, reducing development time and cost.

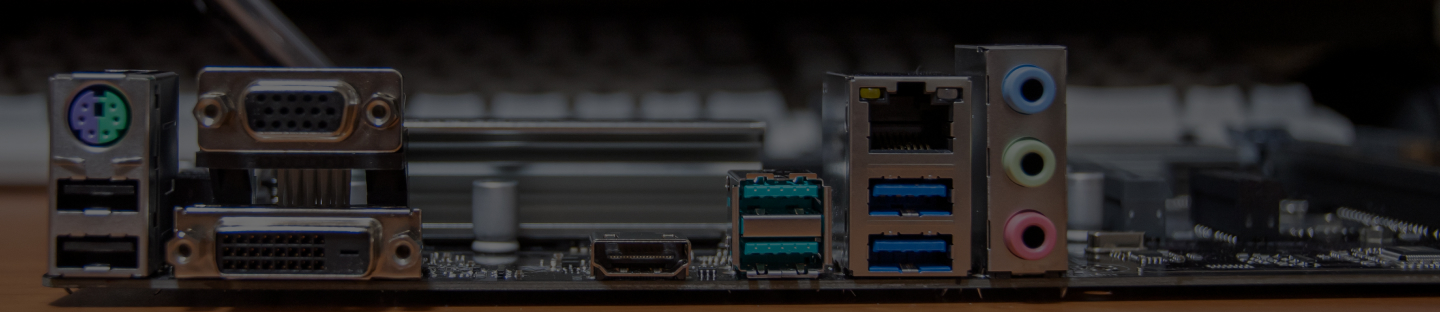

An application IP subsystem typically consists of several components, including a processor, memory, peripherals, and interfaces. The processor is responsible for executing the software that controls the subsystem, while the memory is used to store data and program code. Peripherals are used to interface with external devices, such as sensors and displays, while interfaces provide a standard interface for communication with other subsystems within the SoC.

Application IP subsystems can be designed to be highly customizable and can be optimized for specific use cases. For example, a subsystem designed for audio processing may include specialized DSP hardware, while a subsystem designed for video processing may include hardware accelerators for video decoding and encoding.

The use of application IP subsystems can provide several benefits for SoC design. Firstly, they can help to reduce development time and cost by providing pre-designed and pre-verified solutions for specific functions. Secondly, they can help to reduce the risk of errors and bugs in the design by providing a tested and proven solution. Finally, they can help to improve performance by providing highly optimized solutions that are designed specifically for the intended use case.

In summary, application IP subsystems are a critical component of a System-on-Chip design. They provide pre-designed and pre-verified solutions for specific functions, helping to reduce development time and cost while improving performance and reducing the risk of errors.

Support Activities

Verify subsystem connectivity and basic function

Synthesize all RTL

Create subsystem testbench with standard VIPs or new ones as needed

DFT insertion (scan/lbist, MBIST & ijtag)

Check performance of major interfaces

Place and Route RTL blocks and 3rd party hard macros

Floorplan each subsystem per top level plan

Iterate as necessary for timing closure

Create clock and placement constraints as necessary

Perform RTL/gate equivalence checks

Perform all LVS and DRC

Perform ECOs for SOC timing and floorplan closure and IP