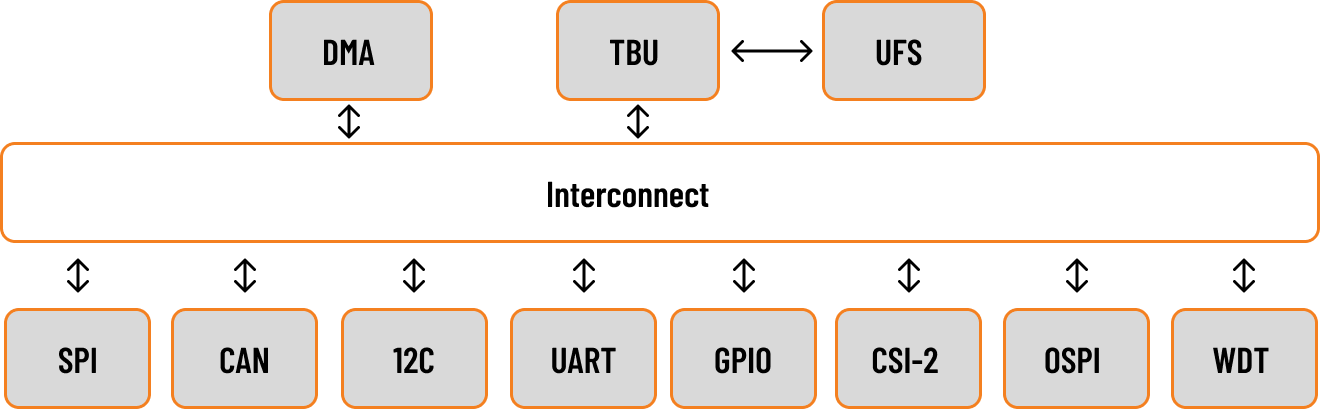

Low Speed I/O Interface

A low-speed IO subsystem refers to the IO interfaces that operate at a lower frequency than the other high-speed interfaces in the SoC. These interfaces typically include UART, SPI, I2C, and other similar interfaces that are used to communicate with slower peripherals such as sensors, displays, and other low-speed devices.

To address the issue of a low-speed IO subsystem, several design techniques can be implemented in the SoC. One approach is to use dedicated hardware blocks that can handle the low-speed interfaces independently, allowing for parallel processing and reducing the overall latency. Another approach is to use intelligent buffering and caching techniques to optimize the data flow and minimize the impact of the slower interfaces on the overall system performance.

In addition to hardware optimizations, software optimizations can also be employed to improve the performance of the low-speed IO subsystem. This can include techniques such as data compression, data aggregation, and prefetching, which can help reduce the number of transactions required and improve the efficiency of data transfers.

Overall, a well-designed low-speed IO subsystem is critical for ensuring optimal system performance in modern SoCs. By employing a combination of hardware and software optimizations, designers can minimize the impact of slower interfaces on system performance and deliver an efficient and reliable system to end-users.

Low speed IO subsystem design containing all the communication IP’s like SPI,I2C,UART,DMA etc.

The interconnect and LS IP’s will work in different clock domains, so there are synchronizers placed between the modules in different domains.

Owning the LSIO subsystem which includes, designing, verification and implementation.

It also has AMBA slave ports connecting to the SoC interconnect.

Support Activities

Verify subsystem connectivity and basic function

Synthesize all RTL

Create subsystem testbench with standard VIPs or new ones as needed

DFT insertion (scan/lbist, MBIST & ijtag)

Check performance of major interfaces

Place and Route RTL blocks and 3rd party hard macros

Floorplan each subsystem per top level plan

Iterate as necessary for timing closure

Create clock and placement constraints as necessary

Perform RTL/gate equivalence checks

Perform all LVS and DRC

Perform ECOs for SOC timing and floorplan closure and IP